Ultra-Low Power (ULP) Timer Architecture#

The Ultra-Low-Power (ULP) Timer block operates within the ULP Subsystem (ULPSS) of the SiWx917 device.

It uses a multiplexer of low-power clock sources such as the reference clock (REF), 32 kHz RC/XTAL, or MHz RC oscillator.

Each of the four timer instances (ULP_TIMER_0 to ULP_TIMER_3) has a dedicated interrupt request (IRQ) line, serviced by a user-defined callback.

The Power Manager can configure any ULP Timer as a wake source, allowing deterministic wake-ups from power-saving states.

This capability enables precise timing and event scheduling during low-power operation.

Key Features#

Feature | Description |

|---|---|

Four independent timers | Each timer can run separately with individual configurations. |

Configurable operation modes | Supports both 32-bit counter and 32-bit microsecond timer modes. |

Dual resolution modes | Operates in 1 µs or 256 µs resolution for flexible timing ranges. |

Integral and fractional programming | Allows fine-grained timing control in either resolution mode. |

One-shot and periodic operation | Run timers once or repeatedly based on application needs. |

Per-timer interrupt enable/disable | Generate interrupts individually for specific timers. |

Asynchronous or synchronous operation | Works independently or synchronized with the SoC clock. |

Note: Use 1 µs mode for fine-grained control and 256 µs mode for extended intervals with minimal power consumption.

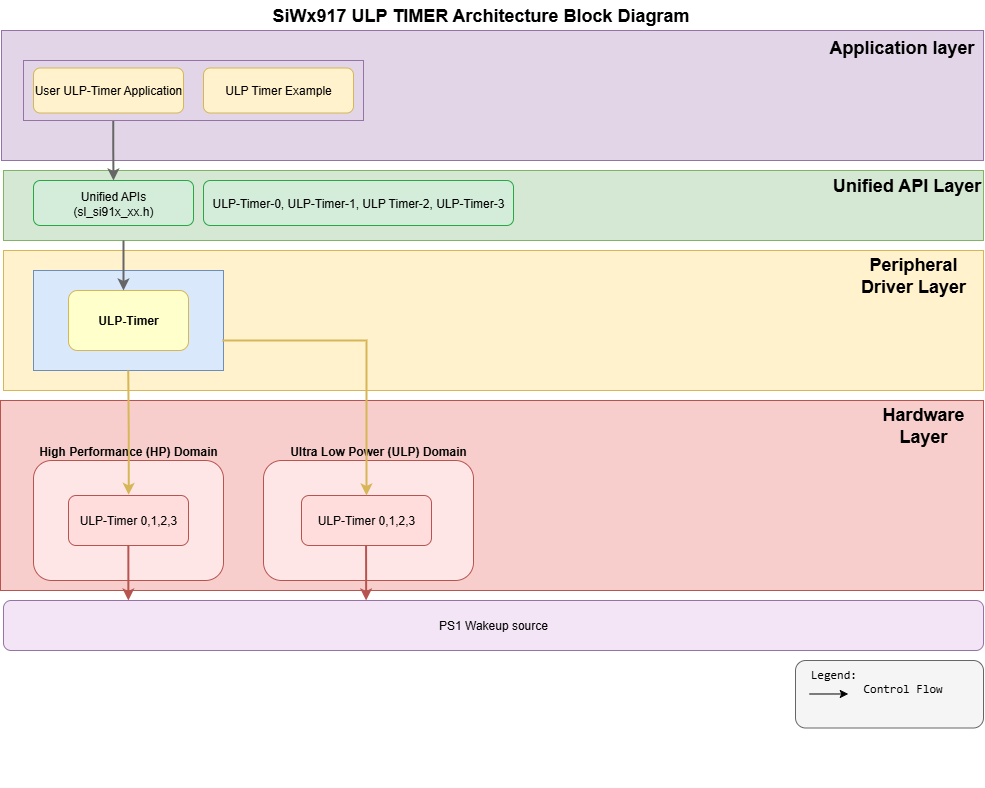

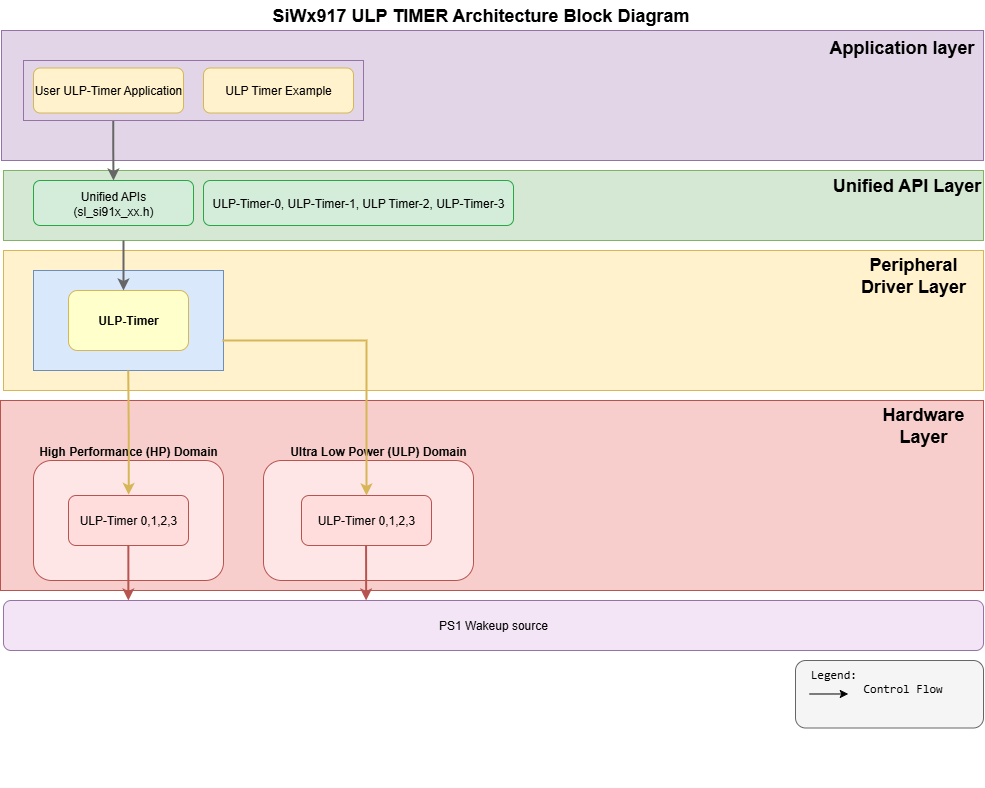

ULP Timer Software Architecture#

The ULP Timer software stack in the WiSeConnect SDK is organized into multiple abstraction layers. This modular design improves clarity, scalability, and maintainability for embedded development.

Figure: ULP Timer software architecture

Core Components#

Layer | Description |

|---|---|

Application Layer | Contains user or example projects that use the ULP Timer API for event scheduling and power-aware timing. |

Unified API Layer | Provides high-level driver APIs for initialization, configuration, and interrupt handling. |

Peripheral Driver Layer | Includes low-level driver logic for register access and hardware control. |

Hardware Layer | Represents the physical ULP Timer peripheral within the SiWx917 SoC. |

This layered approach:

Abstracts low-level hardware complexity through a unified driver API.

Supports modular development, allowing independent testing and updates.

Enables both high-performance and ultra-low-power timing applications.

Integrates seamlessly with the DMA controller for efficient data transfer.

Simplifies debugging and enhances code readability.

Tip: The modular architecture allows firmware teams to reuse the same ULP Timer API across multiple power domains or applications.

Directory Structure in WiSeConnect SDK#

The WiSeConnect SDK follows a consistent folder structure for ULP Timer source files, headers, and examples.

wiseconnect/ ├── components/ │ └── device/ │ └── silabs/ │ └── si91x/ │ └── mcu/ │ └── drivers/ │ └── unified_api/ │ ├── inc/ │ │ └── sl_si91x_ulp_timer.h │ └── src/ │ └── sl_si91x_ulp_timer.c └── examples/ └── si91x_soc/ └── peripheral/ └── sl_si91x_ulp_timer

This directory layout keeps the driver, API headers, and example projects organized consistently across all peripherals in the WiSeConnect SDK.

Clock and Power Management#

In most applications, you do not need to manually configure clock or power settings for the Ultra-Low-Power (ULP) Timer.

Simplicity Studio and the WiSeConnect SDK automatically handle these configurations when you add and set up the ULP Timer component in your project.

For advanced customization or troubleshooting, refer to the following resources:

SiWx917 Hardware Reference Manual – Detailed information on clock domains and power states.

WiSeConnect SDK Documentation – Reference for API behavior, configuration options, and integration details.

ULP Timer Low Power Instance Guide – Steps for advanced low-power setup and optimization.

Note: All four ULP Timer instances are memory-mapped, starting from the base address

0x2404_2000.

Dependencies#

The Ultra-Low-Power (ULP) Timer relies on the following software components and configuration tools for setup, integration, and operation.

Dependency | Purpose |

|---|---|

WiSeConnect SDK | Provides driver source files, header definitions, and peripheral integration for the ULP Timer. |

Simplicity Studio Configuration ( | Includes the ULP Timer components and links them to project build settings. |

Universal Configurator (UC) | Used to define parameters such as clock source, resolution, and timer mode. |

Clock and Divider Settings | Managed through the MCU’s clock system to achieve precise timing and power balance. |

Power Manager | Controls ULP Timer availability and wake-source behavior across low-power states. |

Tip: For a step-by-step configuration guide (including Simplicity Studio setup, UC parameter selection, and code generation), efer to the ULP Timer Initialization and Configuration Guide.