System Real-Time Clock (SYSRTC) Architecture#

The System Real-Time Clock (SYSRTC) on the SiWx917 platform provides a low-frequency, always-on timer for precise timekeeping, wake scheduling, and general-purpose input/output (GPIO) waveform generation.

It operates across all power states (PS4–PS0) and integrates with the always-on low-power subsystem for efficient interrupt handling.

SYSRTC supports:

Programmable clock sources for flexible timing control

Configurable GPIO routing for capture and compare functions

A multi-group architecture that enables independent compare and capture operations within a shared counter

This combination delivers accurate timing and energy-efficient performance for real-time and low-power embedded applications.

Peripheral Overview#

Base Address: 0x2404_8C00

Key Features#

32-bit shared counter for precise timekeeping

32 kHz or 1 kHz operation (1 kHz derived via divider from 32 kHz sources)

Low-energy mode and wake capability

Up to two independent groups for concurrent timing (Groups 0–1 enabled)

One or two compare channels per group for event scheduling

Optional capture channel per group for input event measurement

Optional debug-halting control (run-in-debug selectable)

Software reset for recovery and reinitialization

Continuous operation across all power states, including deep sleep

Flexible GPIO routing for compare outputs and capture inputs

Programmable clock source selection and division (RC/RO/XTAL 32 kHz; 1 kHz via divider)

Advanced interrupt support, including per-group flags and optional alternate IRQ/wakeup

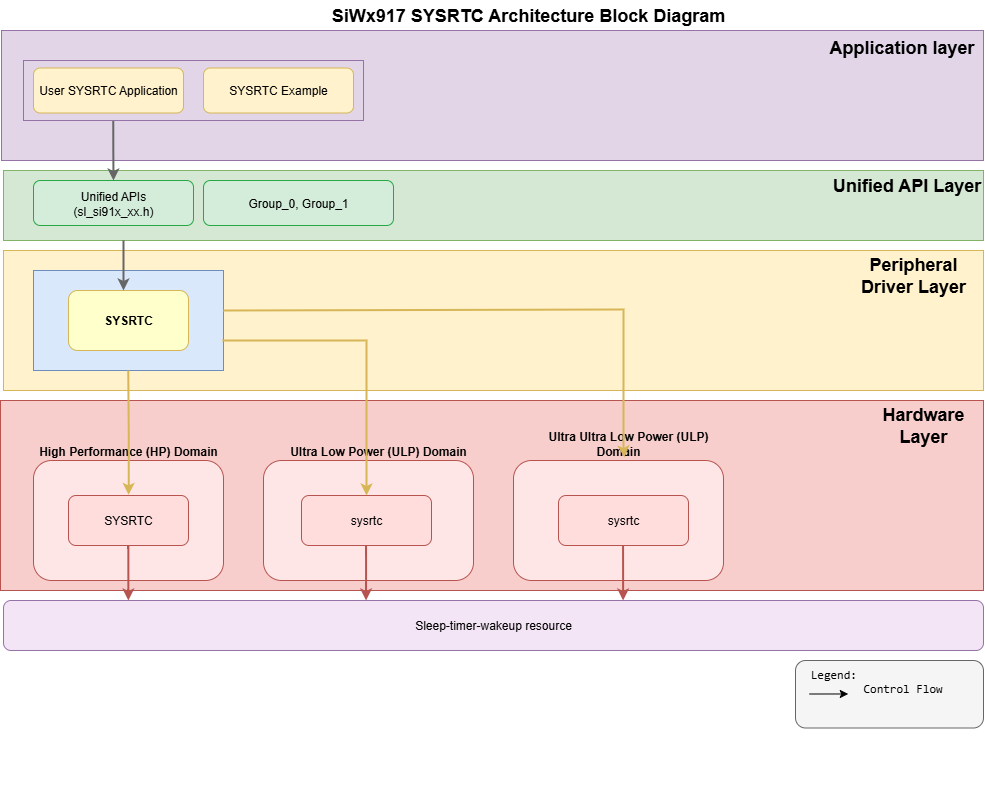

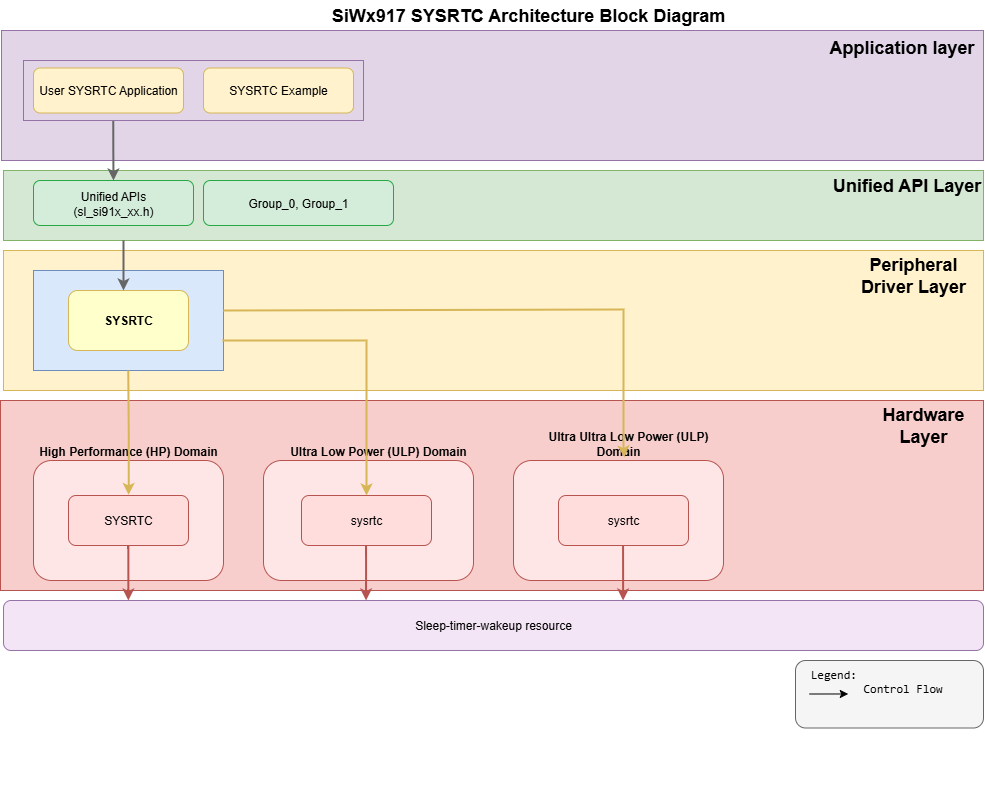

SYSRTC Software Architecture#

The SYSRTC software architecture uses layered abstraction to keep code modular, scalable, and easy to maintain.

Applications configure, control, and monitor SYSRTC through a unified application programming interface (API), while the driver layer manages register-level operations.

This layered design simplifies integration with power management, interrupt handling, and other system services.

Figure: SYSRTC Software Architecture

Core Components#

The SYSRTC software stack includes these layers:

Application Layer: Your application code or examples that call the SYSRTC API.

Unified API Layer: High-level driver APIs for initialization, configuration, and data transfer.

Peripheral Driver Layer: Low-level code for register access and hardware control.

Hardware Layer: The physical SYSRTC peripheral within the SiWx917 system-on-chip (SoC).

This layered design:

Abstracts hardware details behind a single API for all timing operations.

Enables modular development for easy integration, configuration, and maintenance.

Supports high-precision and ultra-low-power timing with dedicated hardware domains and power-management hooks.

Uses interrupts and callbacks for efficient event handling.

Separates concerns so you can understand, extend, and debug timing-centric applications faster.

By following this model, you can build robust, scalable SYSRTC-based solutions on SiWx917.

Directory Structure in WiSeConnect Software Development Kit (SDK)#

wiseconnect/ ├── components/ │ └── device/ │ └── silabs/ │ └── si91x/ │ └── mcu/ │ └── drivers/ │ └── unified_api/ │ ├── inc/ │ │ └── sl_si91x_sysrtc.h │ └── src/ │ └── sl_si91x_sysrtc.c └── examples/ └── si91x_soc/ └── peripheral/ └── sl_si91x_sysrtc

Clock and Power Management#

On SiWx917 devices, the platform and WiSeConnect SDK manage SYSRTC clocking and power automatically:

Always-on 32 kHz sources: SYSRTC runs from dedicated 32 kHz clocks — crystal (XTAL) or RC — that remain active across PS4 through PS0.

Deep-sleep continuity: SYSRTC continues timekeeping, wake scheduling, and event generation in deep-sleep and other ultra-low-power modes.

No manual gating required: You typically don’t modify register-level clock or power settings. When you add the SYSRTC component, Simplicity Studio and the SDK configure the clock sources and power domains for you.

Advanced use and debug: For edge cases (custom board clocks, unusual sleep policies, or troubleshooting), consult the SiWx917 Reference Manual, WiSeConnect SDK documentation, and the SYSRTC low-power guidance for clock domains and power-state integration details.

Power Domain Overview#

SYSRTC resides in the always-on (AON) low-frequency domain, independent of the main MCU power domains. This design keeps SYSRTC running even when high-performance resources are gated.

Active across PS4–PS0: SYSRTC remains operational through PS4, PS3, PS2, PS1, and PS0, including deep-sleep and ultra-low-power modes.

Continuous functionality: Timekeeping, wake scheduling, and event generation are available in both high-performance and low-power operation.

AON-managed clocks: The AON domain manages the 32 kHz clock source (XTAL or RC) so SYSRTC maintains continuous timing and wake capability regardless of overall SoC state.

Dependencies#

WiSeConnect SDK (install and configure in Simplicity Studio)

Simplicity Studio configuration (

.slcp) that includes SYSRTC componentsUniversal Configurator (UC): Set clock source, division, and group/channel enables

Clock-source and divider settings managed through the microcontroller clock architecture

Power-state management (SYSRTC availability across PS4, PS3, PS2, PS1, PS0)

Direct memory access (DMA) buffers (if used) placed in ultra-low-power (ULP) memory for best performance in low-power modes

For step-by-step setup (including installing the SDK, configuring Simplicity Studio, selecting components, using Universal Configurator, and generating code), see the SYSRTC Initialization and Configuration Guide.