M4 Power States#

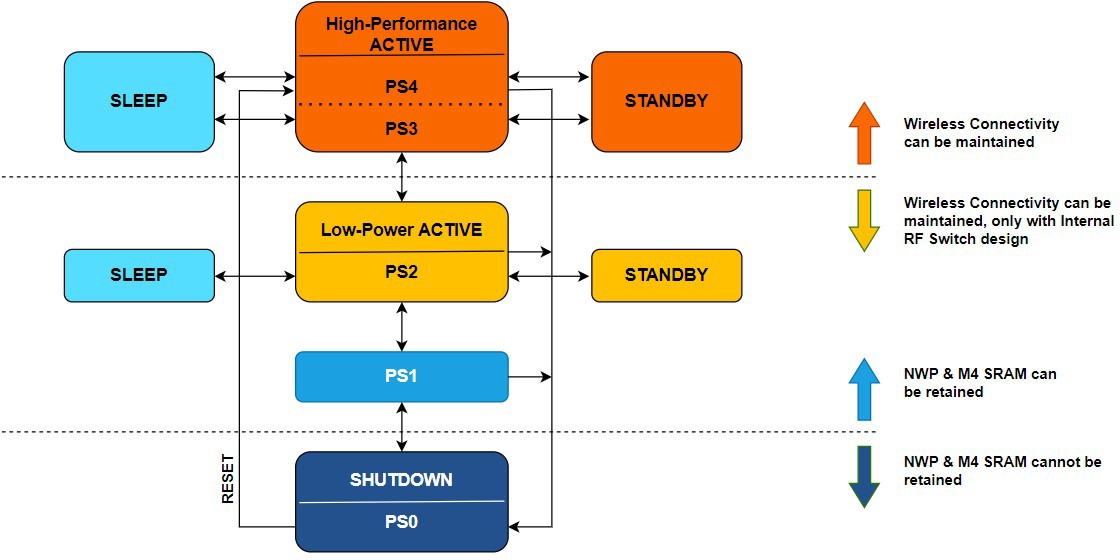

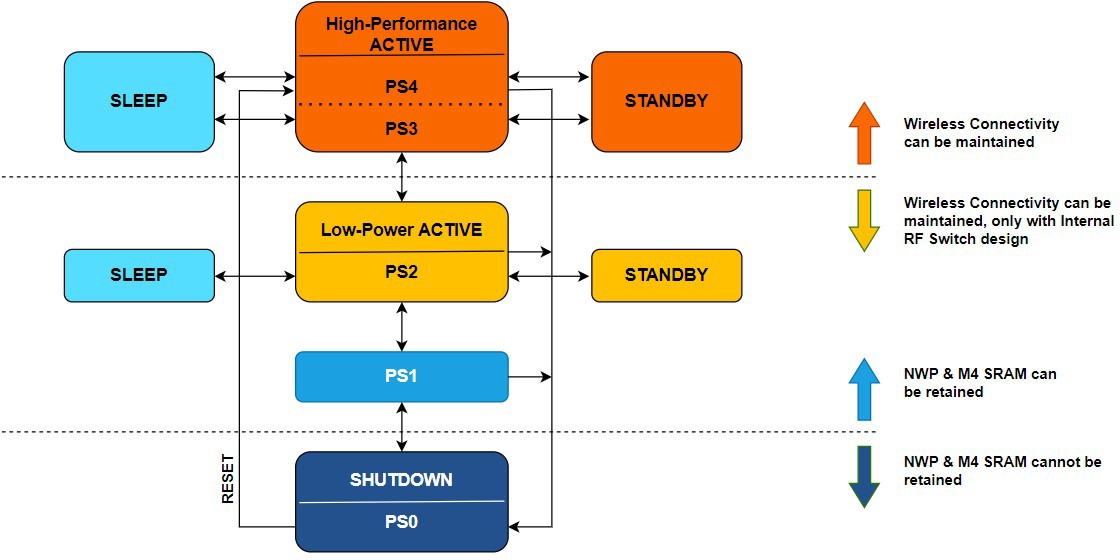

The operational states of the SiWG917 M4 subsystem are called power states (PSx) and are numbered from PS4 to PS0. The PS number is directly proportional to the current consumption. The power states offer different levels of functionality and thus also varying power consumption, allowing designers to scale the resources to fit the bare minimum of what is needed in the application at any given time.

The M4 power states are segregated into power modes as listed below:

Active mode: CPU is powered ON, operating at the configured frequency

Standby mode: CPU is clock-gated, the remaining system operating at the configured frequency

Sleep mode: CPU is power-gated, RAM can be retained

Deep sleep/Shutdown mode: CPU is power-gated, RAM cannot be retained

Active Mode Power States#

The SoC in Active Mode can be in any of the four power states (i.e., PS4/PS3/PS2/PS1).

After reset, the processor starts in the PS4 active state, the highest activity state where full functionality is available. The other active states (PS3/PS2/PS1) will have limited functionality or processing power.

PS4 Active: Highest power consumption state, having complete functionality available for M4

PS3 Active: Complete functionality is available, operating at a lower voltage thereby reducing current consumption

PS2 Active: Limited functionality is available, operating at a much lower voltage compared to PS4 and PS3

PS1: CPU is off, and limited peripherals are powered ON; these peripherals need to be configured for desired functionality before entering this state

The functional characteristics of each of the active modes can be understood using the following table:

| Power States | PS4 Active | PS3 Active | PS2 Active | PS1 |

|---|---|---|---|---|

| CPU operating frequency (max) | 180 MHz | 90 MHz | 20 MHz 32 MHz |

OFF |

| SRAM operating voltage | LDO SoC 1.15 V | LDO SoC 1.05 V | LDO SoC 0.75 V DC-DC 1.05 V |

LDO SoC 0.7 V DC-DC 1.0 V |

| Power domains ON | All | All | Applications ULP peripherals UULP peripherals Analog peripherals |

ULP peripherals UULP peripherals Analog peripherals |

| GPIOs available | SoC GPIOs ULP GPIOs UULP GPIOs |

SoC GPIOs ULP GPIOs UULP GPIOs |

ULP GPIOs UULP GPIOs |

ULP GPIOs UULP GPIOs |

| SRAM powered ON | 320 kB LP SRAM 8 kB ULP SRAM |

320 kB LP SRAM 8 kB ULP SRAM |

320 kB LP SRAM 8 kB ULP SRAM |

320 kB LP SRAM (can be retained but not executable) 8 kB ULP SRAM |

Note: For more information on power domains, refer to Section 9.3.1 of the SiWG917 Hardware Reference Manual.

Standby States#

The M4 in Standby Mode can be in three power states (i.e., PS4-Standby, PS3-Standby, and PS2-Standby). Each power state can be entered from its respective active state using the Wait For Interrupt (WFI) instruction.

The functional characteristics of this mode include the following:

CPU clock-gated

SRAM operates at the same voltage as its respective active state

Peripherals, GPIOs and SRAM available are same as its respective active state

Any interrupt can be used as a wakeup source in the Standby mode to achieve the transition from Standby mode to Active mode.

Sleep States#

The M4 in Sleep Mode can be in three states, i.e., PS4-Sleep, PS3-Sleep, and PS2-Sleep. Each power state can be entered from its respective active state using software instruction.

The functional characteristics of this mode include the following:

CPU power-gated

UULP peripherals are functional. Peripherals need to be configured for desired functionality, before entering this state.

UULP-VBATT GPIOs are powered ON

320 kB LP-SRAM can be retained

Deepsleep/Shutdown Mode#

PS0, also known as deepsleep state, can be entered from any active state through software instruction. Wakeup from PS0 resets the chip, followed by PS4 active state.

The functional characteristics of this mode include the following:

CPU power-gated

UULP peripherals are functional and need to be configured before entering this state

UULP-VBATT GPIOs are powered ON

SRAM cannot be retained

The flowchart below gives an overview on the power state transitions, CPU, and SRAM configurations available in various power states.

A transition from active states to any other state can be triggered through software.

A transition from Standby/Sleep/Shutdown state can be triggered by an enabled interrupt as configured by software before entering the state.