System Overview#

The SiWG917 (SoC) contains different power modes for M4 and NWP, providing flexibility in selecting the power state combination at different stages in a product life cycle.

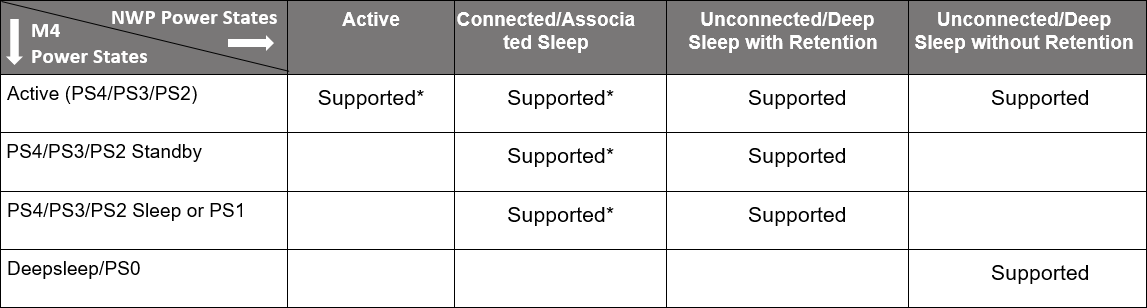

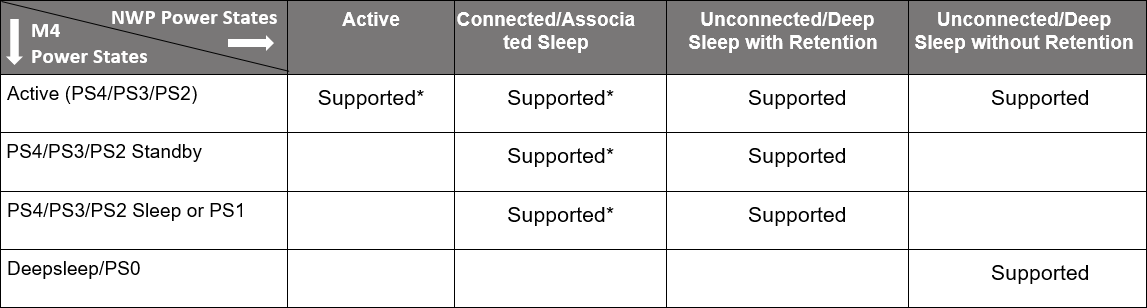

The SoC low-power compatibility matrix can be illustrated as below:

SiWG917 M4 vs NWP Power Modes Compatibility Matrix#

M4 is in PS2/PS1 with NWP in Active/Connected Sleep combination, is only supported in Internal RF Switch design. This power mode combination is not supported in External RF Switch design.

Note: Part of M4 application should be configured to execute from SRAM during M4 sleep-wakeup transitions since the flash is turned OFF during sleep, and when M4 is in PS2 or lower states since the QSPI peripheral is turned OFF, more details in the upcoming sec-tions.

There are few exceptions related to M4:

M4 in PS2 Active and NWP in Unconnected Sleep with/without Retention.

M4 in PS2 Active/Standby/Sleep and NWP in Active/Connected Sleep is not supported.