PSRAM Driver#

Introduction#

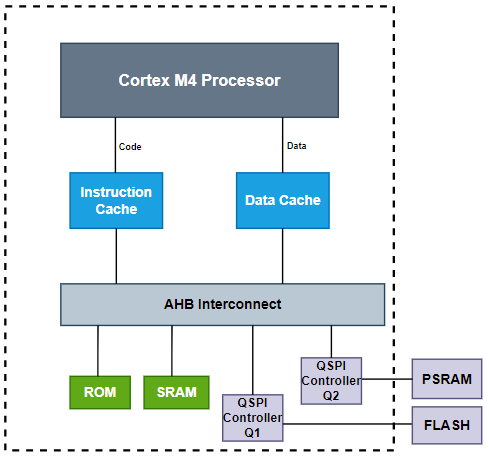

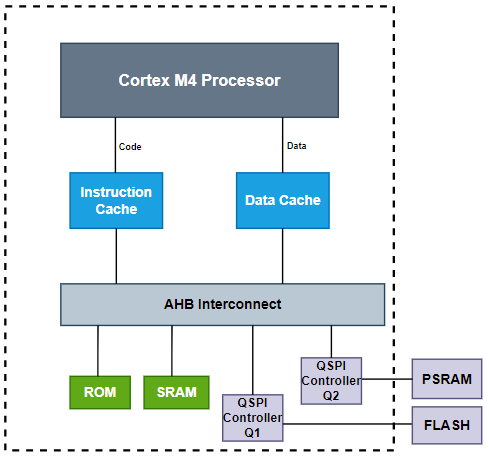

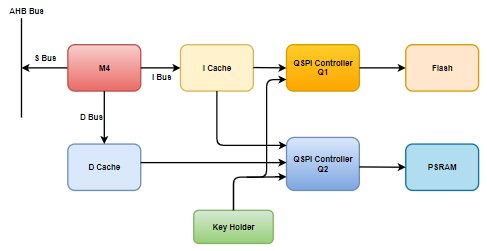

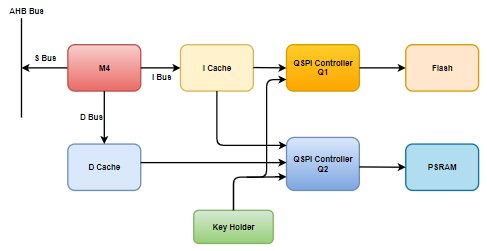

PSRAM (Pseudo Static Random Access Memory) is a random-access memory whose internal structure is based on dynamic memory with refresh control signals generated internally, in the standby mode, so that it can mimic the functionality of a static memory. It combines the high density of DRAM with the ease-of-use of true SRAM. The M4 core communicates with the PSRAM via Quad SPI interface.

To enhance performance, PSRAM access is optimized through a cache memory system. This "Modified Harvard Architecture" allows the core to access instructions and data through separate caches (Data cache and Instruction cache), which then access the common PSRAM. When data is already in the cache ("Cache Hit"), it’s quickly provided to the core. If not ("Cache Miss"), the cache retrieves the data from PSRAM, improving overall performance.

The architecture is designed to ensure efficient memory access, with the data path supported by a 16KB, 4-way set associative cache with a 32-byte cache line. The instruction path leverages the existing instruction cache shared between flash and PSRAM.

Configuration#

PSRAM Device Configuration#

The PSRAM Driver offers configuring the following:

Read-Write type

Normal: This is supported only in SPI interface mode. Supports a maximum frequency of 33MHz. Uses normal read and normal write commands.

Fast: Supported in SPI and QPI mode. Uses fast read and normal write.

Quad IO: Supported in SPI and QPI mode. Uses fast quad read and write.

Interface mode

SPI Mode (Serial IO)

QPI Mode (Quad IO)

Linker configurations#

The text segment, data segment, bss, heap, and stack can be placed in PSRAM by installing the respective components present under "PSRAM Linker Configurations" from the "SOFTWARE COMPONENTS" GUI. Since PSRAM is already initialized in the bootloader, these components can be installed and the respective segments can be placed in PSRAM without installing the "PSRAM Core" component and without initializing PSRAM from the application.

For more information on configuring available parameters, see the respective peripheral example readme document.

Usage#

The PSRAM Driver and QSPI are initialized by the bootloader with Quad IO read-write type and QPI interface. The application is not required to reinitialize the PSRAM device and QSPI unless the configurations required are different from the default set by the bootloader.

The PSRAM device handle "PSRAM_Device" of type sl_psram_info_type_t is defined in "sl_si91x_psram_handle.c".

sl_si91x_psram_uninit assumes that PSRAM was initialized with QPI mode and exits QPI mode within the definition. If the PSRAM configuration in the boot code has SPI mode enabled, the user is expected to comment out the exit QPI mode function call in sl_si91x_psram_uninit.

To reconfigure and initialize PSRAM, set the required configurations from the PSRAM Core component and call sl_si91x_psram_init within the application.

Modules#

PSRAM Chip Select and Base Address

Enumerations#

PSRAM return error code.

Functions#

To configure and initialize the PSRAM Device.

To uninitialize the PSRAM Device.

To reset the PSRAM Device.

To write data to PSRAM in manual mode.

To read data from PSRAM in manual mode.

To write data to PSRAM in manual mode using DMA.

To read data from PSRAM in manual mode using DMA.

To put the PSRAM device in sleep mode.

To exit the PSRAM device from sleep mode.

To enable CTR encryption-decryption on PSRAM.

Enumeration Documentation#

sl_psram_return_type_t#

sl_psram_return_type_t

PSRAM return error code.

| Enumerator | |

|---|---|

| PSRAM_SUCCESS | No error. |

| PSRAM_FAILURE | Generic error. |

| PSRAM_UNKNOWN | Unknown request. |

| PSRAM_UNKNOWN_DEVICE | Unknown PSRAM Device. |

| PSRAM_CLOCK_INIT_FAILURE | Clock init failure. |

| PSRAM_NOT_INITIALIZED | PSRAM not initialized. |

| PSRAM_SUPPORTED_DEVICE | PSRAM Device supported. |

| PSRAM_DEVICE_MISMATCH | PSRAM Device mismatch. |

| PSRAM_INVALID_HSIZE | Invalid size of element. |

| PSRAM_NULL_ADDRESS | Null address. |

| PSRAM_INVALID_ADDRESS_LENGTH | Invalid address length. |

| PSRAM_AUTO_MODE | PSRAM Auto mode. |

| PSRAM_MANUAL_MODE | PSRAM Manual mode. |

| PSRAM_UNSUPPORTED_SECURITY | Unsupported security. |

| PSRAM_MAX_SEC_SEGMENT_REACH | Maximum secure segment reached. |

sl_psram_burst_size_type_t#

sl_psram_burst_size_type_t

Wrap burst size enum.

| Enumerator | |

|---|---|

| _WRAP16 | Burst wrap size 16 Bytes. |

| _WRAP32 | Burst wrap size 32 Bytes. |

| _WRAP64 | Burst wrap size 64 Bytes. |

| _WRAP512 | Burst wrap size 512 Bytes. |

sl_psram_dma_status_type_t#

sl_psram_dma_status_type_t

PSRAM DMA status enum.

| Enumerator | |

|---|---|

| DMA_NONE | DMA status default. |

| DMA_DONE | DMA transfer completed. |

| DMA_FAIL | DMA transfer failed. |

Function Documentation#

sl_si91x_psram_init#

sl_psram_return_type_t sl_si91x_psram_init (void )

To configure and initialize the PSRAM Device.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| void | N/A |

Returns

Status code indicating the result.PSRAM_SUCCESS: Initialization successful

PSRAM_FAILURE: Initialization failed

Note

The configurations for initialization are taken from the PSRAM Device config header file. The selection of the configuration file happens implicitly based on the radio board selection.

sl_si91x_psram_uninit#

sl_psram_return_type_t sl_si91x_psram_uninit (void )

To uninitialize the PSRAM Device.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| void | N/A |

Returns

Status code indicating the result.PSRAM_SUCCESS: Uninitialization successful

PSRAM_FAILURE: Uninitialization failed

sl_si91x_psram_reset#

sl_psram_return_type_t sl_si91x_psram_reset (void )

To reset the PSRAM Device.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| void | N/A |

Returns

Status code indicating the result.

PSRAM_SUCCESS: Reset successful

PSRAM_FAILURE: Reset failed

sl_si91x_psram_manual_write_in_blocking_mode#

sl_psram_return_type_t sl_si91x_psram_manual_write_in_blocking_mode (uint32_t addr, void * SourceBuf, uint8_t hSize, uint32_t length)

To write data to PSRAM in manual mode.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| uint32_t | [in] | addr | PSRAM address for the write operation |

| void * | [in] | SourceBuf | Reference to the source buffer |

| uint8_t | [in] | hSize | Size of each element |

| uint32_t | [in] | length | Number of elements for the write operation |

Returns

Status code indicating the result.

PSRAM_SUCCESS: Write operation successful

PSRAM_FAILURE: Write operation failed

sl_si91x_psram_manual_read_in_blocking_mode#

sl_psram_return_type_t sl_si91x_psram_manual_read_in_blocking_mode (uint32_t addr, void * DestBuf, uint8_t hSize, uint32_t length)

To read data from PSRAM in manual mode.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| uint32_t | [in] | addr | PSRAM address for the read operation |

| void * | [in] | DestBuf | Size of each element |

| uint8_t | [in] | hSize | Number of elements for the read operation |

| uint32_t | [out] | length | Reference to the destination buffer |

Returns

Status code indicating the result.

PSRAM_SUCCESS: Read operation successful

PSRAM_FAILURE: Read operation failed

sl_si91x_psram_manual_write_in_dma_mode#

sl_psram_return_type_t sl_si91x_psram_manual_write_in_dma_mode (uint32_t addr, void * SourceBuf, uint8_t hSize, uint32_t length, sl_psram_dma_status_type_t * dmaStatus)

To write data to PSRAM in manual mode using DMA.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| uint32_t | [in] | addr | PSRAM address for the write operation |

| void * | [in] | SourceBuf | Reference to the source buffer |

| uint8_t | [in] | hSize | Size of each element |

| uint32_t | [in] | length | Number of elements for the write operation |

| sl_psram_dma_status_type_t * | [out] | dmaStatus | DMA operation completion status |

Returns

Status code indicating the result.

PSRAM_SUCCESS: Write operation successful

PSRAM_FAILURE: Write operation failed

sl_si91x_psram_manual_read_in_dma_mode#

sl_psram_return_type_t sl_si91x_psram_manual_read_in_dma_mode (uint32_t addr, void * DestBuf, uint8_t hSize, uint32_t length, sl_psram_dma_status_type_t * dmaStatus)

To read data from PSRAM in manual mode using DMA.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| uint32_t | [in] | addr | PSRAM address for the read operation |

| void * | [out] | DestBuf | Reference to the destination buffer |

| uint8_t | [in] | hSize | Size of each element |

| uint32_t | [in] | length | Number of elements for the read operation |

| sl_psram_dma_status_type_t * | [out] | dmaStatus | DMA operation completion status |

Returns

Status code indicating the result.

PSRAM_SUCCESS: Read operation successful

PSRAM_FAILURE: Read operation failed

sl_si91x_psram_sleep#

sl_psram_return_type_t sl_si91x_psram_sleep (void )

To put the PSRAM device in sleep mode.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| void | N/A |

Sleep mode is a feature that puts the PSRAM device in an ultra-low power state, while retaining the stored data.

Returns

Status code indicating the result.

PSRAM_SUCCESS: Sleep mode enabled successfully

PSRAM_FAILURE: Failed to enable sleep mode

sl_si91x_psram_wakeup#

sl_psram_return_type_t sl_si91x_psram_wakeup (void )

To exit the PSRAM device from sleep mode.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| void | N/A |

Returns

Status code indicating the result.

PSRAM_SUCCESS: Wakeup successful

PSRAM_FAILURE: Wakeup failed

Note

This function call re-initializes the PSRAM device after the wakeup sequence.

sl_si91x_psram_enable_encry_decry#

sl_psram_return_type_t sl_si91x_psram_enable_encry_decry (uint16_t keySize)

To enable CTR encryption-decryption on PSRAM.

| Type | Direction | Argument Name | Description |

|---|---|---|---|

| uint16_t | [in] | keySize | Pass 128/256-bit size |

Returns

Status code indicating the result.

PSRAM_SUCCESS: Encryption-decryption enabled successfully

PSRAM_FAILURE: Failed to enable encryption-decryption