Sleep State Operational Mode#

The SiWx917’s Sleep state Operational Mode is called Ultra Low Power (ULP) Mode with RAM Retention.

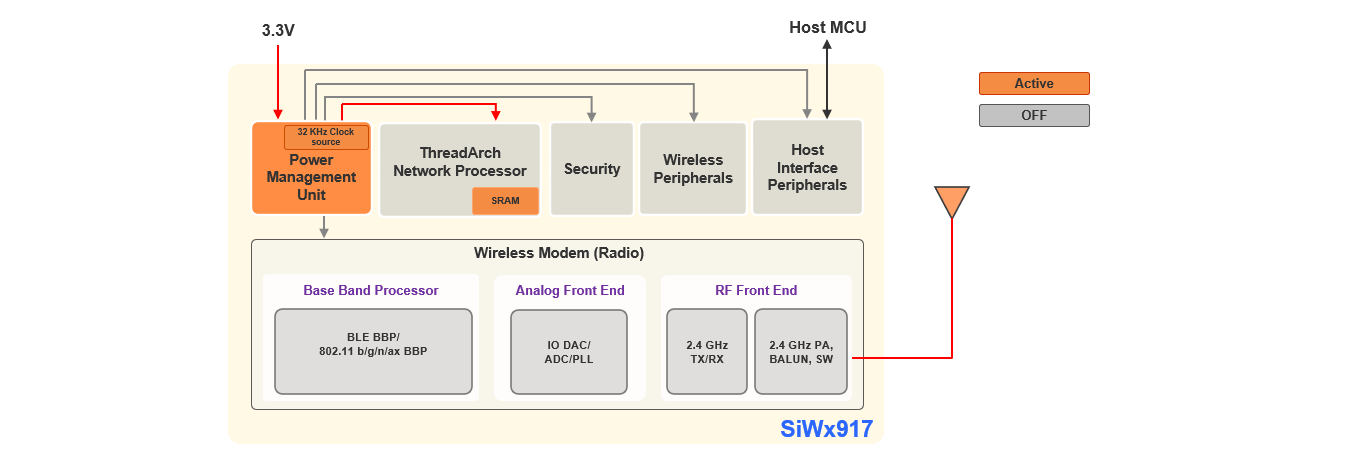

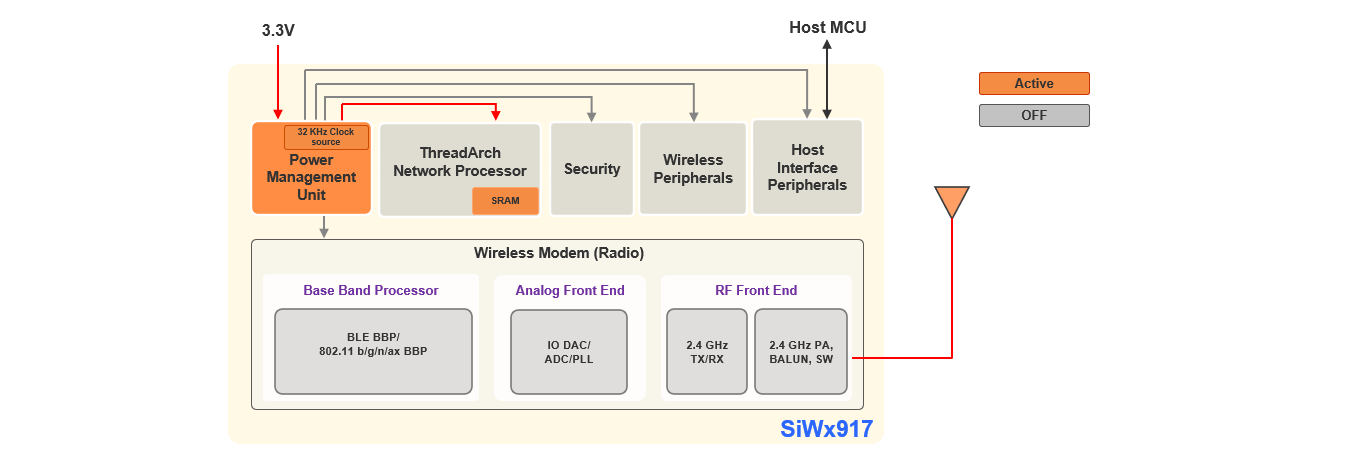

In the Ultra Low Power Mode with RAM Retention, the Wireless Modem, NWP, Security, Wireless Peripherals and Host Interface power domains are powered off. The SRAM contents and its current state are retained.

The PMU has control over the other sections of the chip.

The always-on logic domain operates on a lowered supply and a 32 KHz low-frequency clock to reduce power consumption.

Software Configuration: The 32 KHz Clock Source required during ULP Mode is software configurable. The possible options are:

Internal 32KHz RC clock (default)

32 KHz external crystal clock (enable BIT(22))

32 KHz bypass clock on UULP_VBAT_GPIO_3 (enable BIT(23))

Based on your choice, enable the respective bit in the boot configuration (sl_wifi_device_configuration_t.boot_config.ext_custom_feature_bit_map). For more details on 32 KHz Clock Source, refer to the Clock Specification section in the SiWx917 NCP Data Sheet and Chip Schematic.

The SiWx917 NCP's Host Interface is inactive and thereby the interface is activated each time SiWx917 wakes up.