Static Random Access Memory (SRAM)#

Static random-access memory is static and volatile. Data retention persists as long as the device is powered on. After the power is turned off, data will be lost. Random access memory means that the next memory location that is to be read or written does not depend on the last access location.

The static property comes from its use of a feedback mechanism to maintain the stored bit state. This contrasts with other forms of memory such as dynamic random-access memory (DRAM), where the stored state of the bit is kept in the form of a charge that leaks over time, thereby requiring the data to be refreshed.

Features:

672 KB total SRAM shared between NWP and M4 available.

Fixed configurations for NWP and M4.

Privilege to the user to choose the configuration.

Total memory is divided into smaller banks so that only accessed banks will consume power.

Each bank has its own clock gating input to reduce power consumption.

Tightly coupled to M4 core.

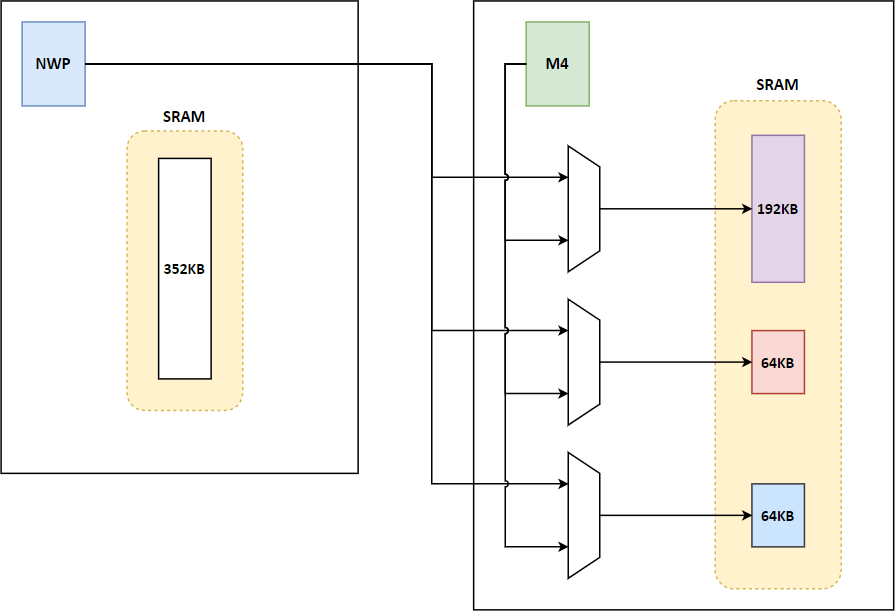

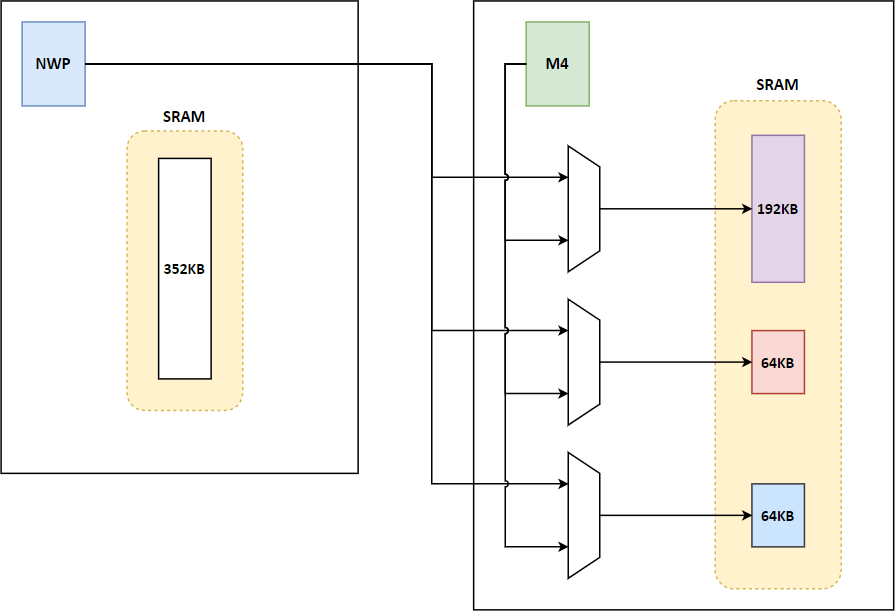

Access Diagram#

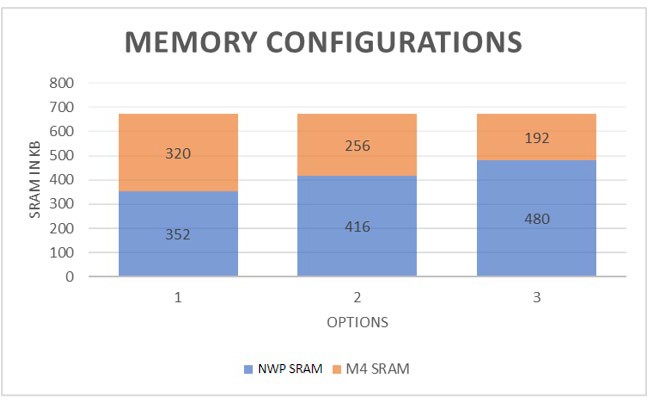

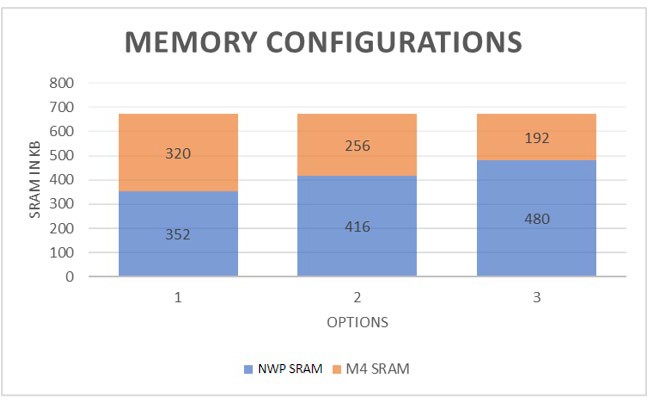

Memory Configurations#

A total of 672 KB of SRAM is available in SiWG917. The available SRAM is shared between NWP and M4. Users can choose the required configuration from the fixed options available based on their application. The configurations are as mentioned below:

For example, if the user application is large and M4 needs more space, then 352 KB for NWP and 320 KB for M4 configuration would be a good choice. If the wireless features are more and the NWP needs more share of RAM, 480 KB for NWP and 192 KB for M4 may be a good choice.

Note: You can configure the SRAM through the Memory Configuration section in the Software Components of your application’s .slcp file.