Configurations in M4 Sleep#

The following configurations can be applied for M4 sleep. You can set these configurations with the Universal Configurator (UC) or manually by using the Power Manager APIs.

RAM Retention#

RAM retention is a low-power mechanism that allows selective SRAM banks to remain powered during M4 Sleep or low-power states such as PS2 and Sleep. This enables the system to preserve critical data (for example, task context, variables, and buffers) without requiring a full reboot after wake-up.

Note: The Power Manager automates the retention setup and recovery through the

sl_si91x_power_manager_configure_ram_retention()API and its usage is given in Reference Guide. Developers can choose to retain memory by size (for example, 64 KB) or by bank number (for example, Banks (SL_SI91X_POWER_MANAGER_M4SS_RAM_BANK_x)).

See the Memory Map Application Note to get the details on the SiWG917 M4 and Network Wireless Processor (NWP) memory split.

In PS2 mode, the SiWG917 M4 operates at a reduced 20 MHz frequency with flash turned off while the Power Manager automatically retains only essential RAM banks (such as FreeRTOS kernel objects, stack, and interrupt buffers), so the CPU can run entirely from RAM without accessing flash.

You can store the application configurations which are required in PS2 state. For this, use the linker file to define memory regions and map the application files from text sections to the data section.

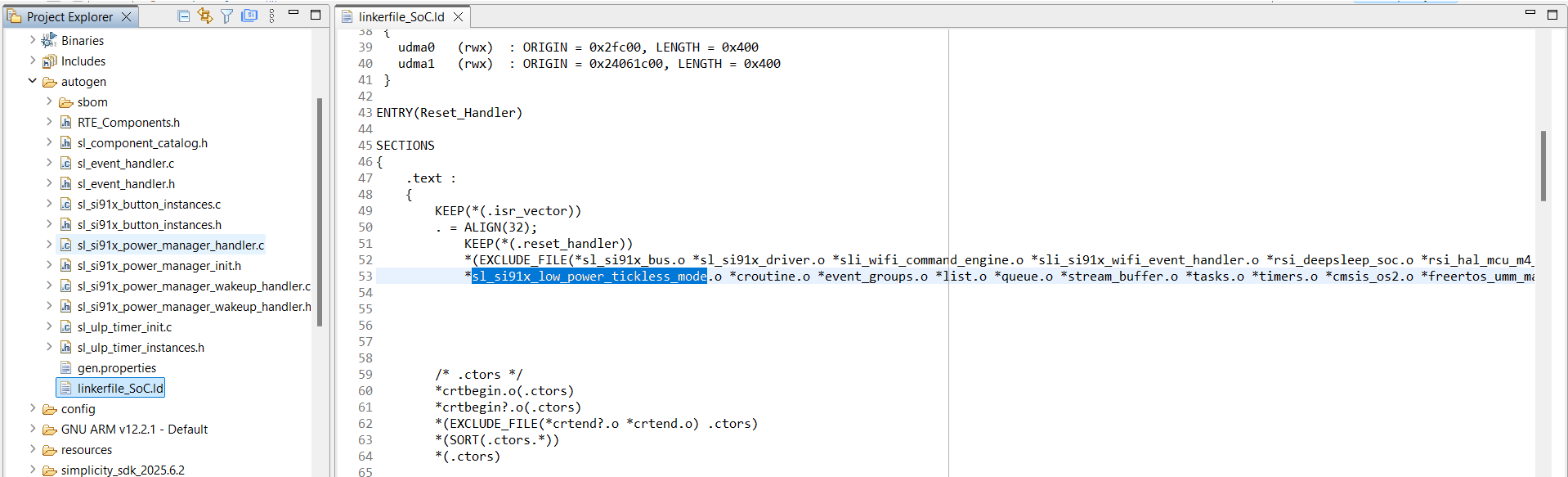

The application file should be removed from the .text section as shown below:

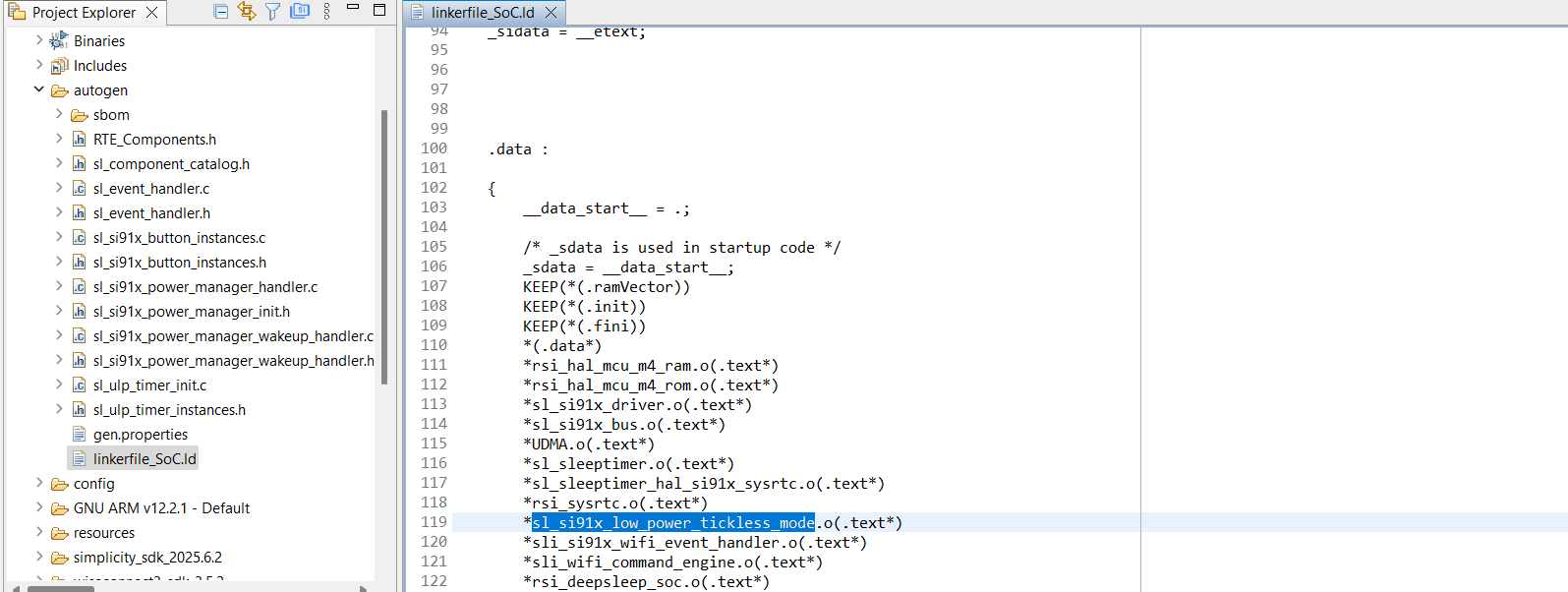

And added to the .data section as shown below:

During M4 sleep, the M4 core and High-Performance (HP), Ultra-Low-Power (ULP) subsystems power down while the Ultra-Ultra-Low-Power (UULP) domain remains active to detect wake-up events. By default, only selected RAM banks are retained to preserve essential data such as stack, variables, network buffers, and task context for wake-up and resume.

See the Power Manager Configuration section in Power Manager Application Note for configuring the RAM retention via UC.

Wake-Up Sources#

A wake-up source is any hardware or software event that can bring the M4 core out of a power-save state (Standby, Sleep, or Deep-Sleep/PS0) and resume code execution. Wake-up sources on SiWx917 include UULP, General-Purpose Input/Output (GPIO), System Real-Time Counter (SYSRTC) alarms, the Deep-Sleep Timer, and Network Wireless Processor (NWP) events (if enabled).

See the Wake-Up Sources section in the SiWG917 data sheet for details on wake-up sources available in PS1, Standby, Sleep, Shutdown states.

Use sl_si91x_power_manager_set_wakeup_sources() to enable/disable sources. Multiple sources can be combined in a single call using a logical OR operation.

Note: When configuring a wake-up source, you must initialize that peripheral manually (for example, configure Network Power and Sleep Subsystem (NPSS) GPIO or SYSRTC). Power Manager marks it as a wake-up source and reapplies the wake-up configuration after resuming.

See the Power Manager Configuration section in Power Manager Application Note for configuring the wake-up source via UC.

Callbacks#

Wake-up source callbacks execute when the system exits a low-power sleep state in response to a configured trigger, such as a GPIO event, calendar alarm, or timer expiration. These callbacks are automatically registered during the configuration of the respective wake-up source through the UC interface.

Each wake-up source is associated with a dedicated callback function. These functions enable the application to resume its operations, process incoming inputs, or manage time-sensitive tasks following the wake-up event.

// GPIO wakeup callback

__attribute__((weak)) void gpio_uulp_pin_interrupt_callback(void)

{

// Handle wake-up initiated by GPIO interrupt

// Inspect GPIO pins and process corresponding input actions

}

// Calendar alarm wakeup callback

__attribute__((weak)) void calendar_alarm_callback_function(void)

{

// Handle wake-up triggered by calendar alarm

// Resume pending scheduled tasks and process time-driven events

}

// Calendar second callback

__attribute__((weak)) void calendar_second_callback_function(void)

{

// Process calendar second tick interrupt

// Update displayed time and perform time-dependent tasks

}

// Deep Sleep Timer callback

__attribute__((weak)) void dst_callback_function(void)

{

// Handle wake-up triggered by Deep Sleep Timer

// Resume pending tasks and update time-driven operations

}To use these callbacks:

Implement the callback function within your application code.

Configure the desired wake-up source through the UC.

The Power Manager automatically handles the registration of the callback.

void dst_callback_function(void)

{

// Run custom application logic

// Continue scheduled tasks and update time-dependent functions

}Ensure that each callback function adheres to the required signature and is defined prior to configuring the wake-up source.

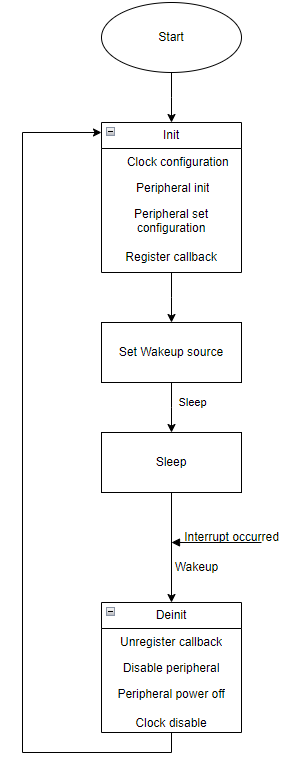

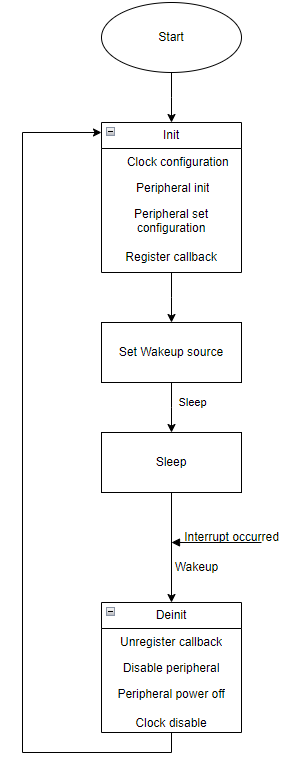

Managing Peripherals#

Peripherals are categorized as follows:

High-Power (PS4/PS3 domain) For example, Serial Peripheral Interface (SPI), Universal Asynchronous Receiver/Transmitter (UARTs), Inter-Integrated Circuit (I²C), Quad Serial Peripheral Interface (QSPI) interface to NWP, etc.

Low-Power (PS2 domain) – DMA (micro-DMA), I²C (primary/secondary), SPI (primary), UART, timers.

Ultra-Low-Power (UULP domain) – SYSRTC/Calendar, UULP GPIO, Watchdog Timer (WDT).

Tip: De-initialize and re-initialize peripherals not retained in sleep upon wakeup, before resuming application tasks.

Power Manager provides an interface to power on and off particular peripherals. Power the peripherals on and off using sl_si91x_power_manager_add_peripheral_requirement and sl_si91x_power_manager_remove_peripheral_requirement respectively with the valid peripherals (m4ss_peripheral, ulpss_peripheral, npss_peripheral) passed in the structure.

Note in UC: The Power Manager Configuration and Advanced Configuration components let you choose which peripherals are powered on or off per domain and also set RAM retention options. Disabling QSPI in the High-Power domain disables M4 ↔ Trusted Application (TA) communication.

Clock Configurations#

Clock scaling allows the M4 core frequency to adjust dynamically between Performance and Power-Save modes based on the current power state. Configure this using the API sl_si91x_power_manager_set_clock_scaling(sl_clock_scaling_t mode). Possible values for clock scaling are listed in the API documentation.

The clock used during SiWG917 M4 sleep is a 32 kHz low-frequency clock.

Note: Clock scaling transitions occur automatically based on the active power-state requirement. Manual scaling (via

set_clock_scaling) overrides this behavior until another PS requirement is added or removed.

Clock Adjustment on Power-State Change

When an add or remove power-state requirement API is invoked, the Power Manager automatically adjusts the CPU and system clocks to the corresponding frequency for that state. For example:

Adding a lower-power state requirement (for example, PS3 → PS2) scales down the clock frequency and may switch to a lower-frequency clock.

Removing the lower-power requirement (for example, PS2 → PS4) restores the previous high-performance clock setting.

This ensures safe transitions between Active and low-power states without user intervention.

Note: During Sleep mode on the SiWG917, the device operates on a 32 kHz low-frequency clock to reduce power consumption.