M4 Power Save#

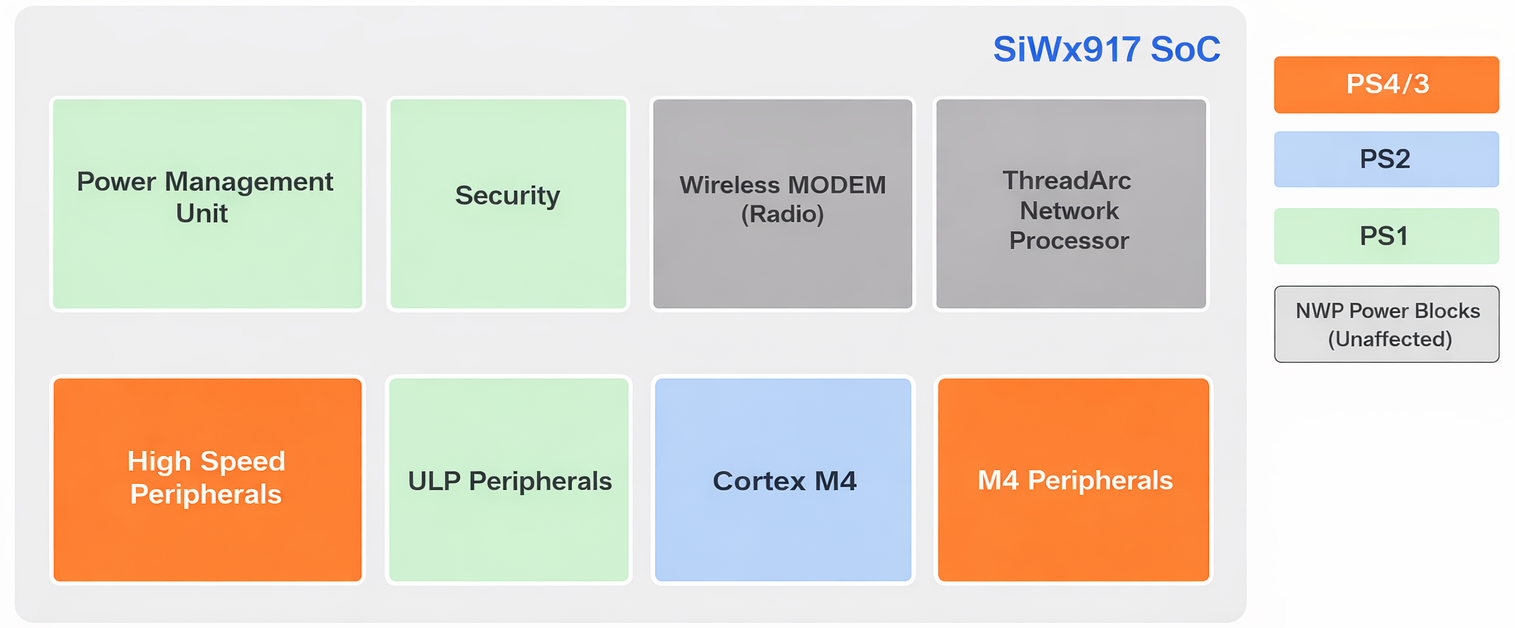

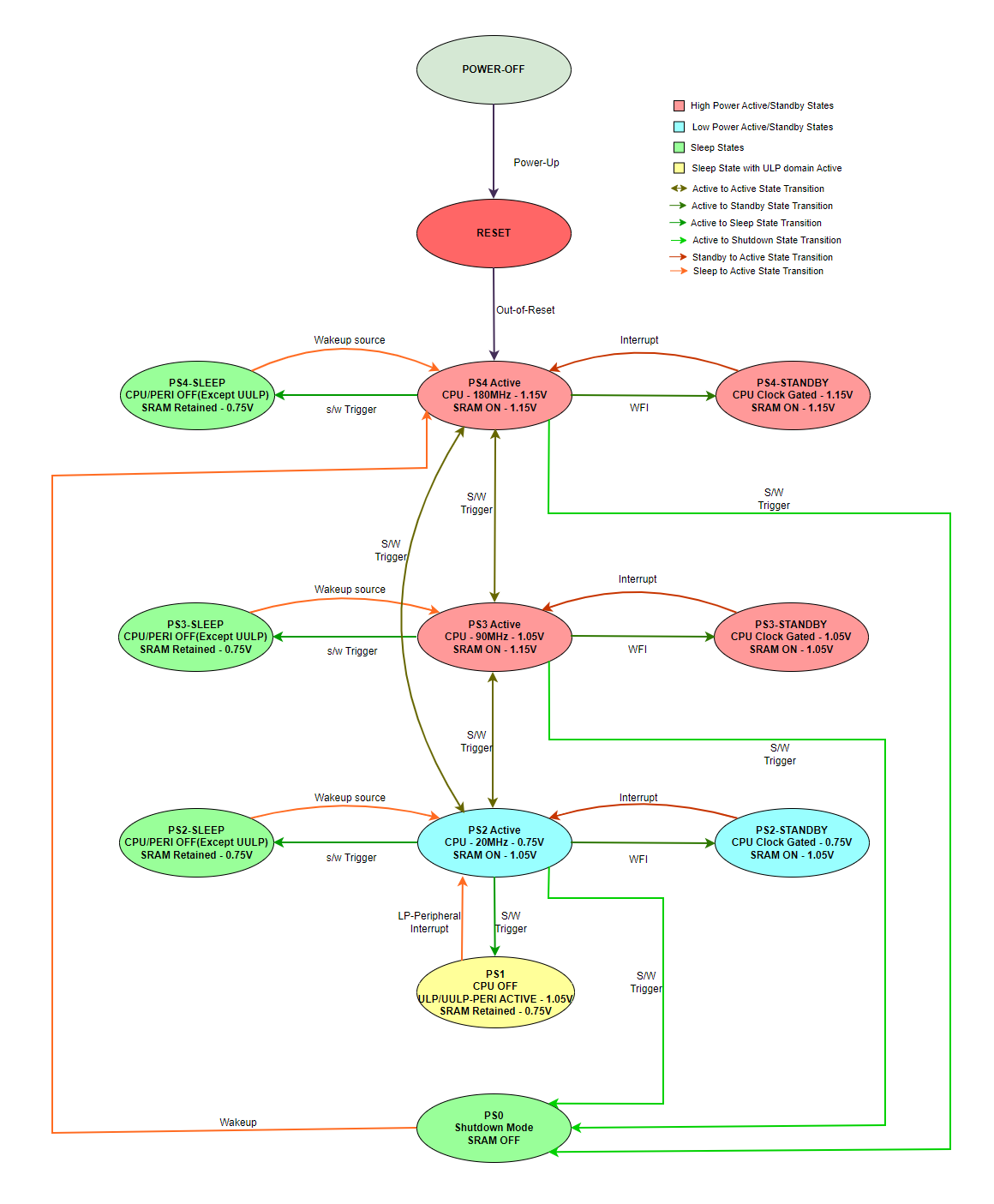

The operational states of the SiWx917 M4 sub-system are called Power States (PSx) and are numbered from PS0 to PS4. The Power States offer different levels of functionality and thus also varying power consumption. Allowing designers to scale the resources to fit the bare minimum of what is needed in the application at any given time.

The M4 power states are grouped into the following power modes:

Active mode: The CPU is powered on and runs at the configured frequency.

Standby mode: The CPU is clock‑gated while the rest of the system continues to operate at the configured frequency.

Sleep mode: The CPU is power‑gated, and RAM can be retained.

Deep Sleep/Shutdown mode: The CPU is power‑gated, and RAM cannot be retained.

Active Mode Power States#

The SoC supports four Active Mode power states: PS4, PS3, PS2, and PS1. After reset, the processor starts in PS4 Active, which provides the highest performance and full functionality. Lower Active states (PS3/PS2/PS1) will have limited functionality or processing power.

PS4 Active: Highest power consumption state; full functionality available for M4.

PS3 Active: Full functionality available at a lower voltage, reducing current consumption.

PS2 Active: Limited functionality; operates at a lower voltage than PS4 and PS3.

PS1: CPU is off; only selected peripherals remain powered. Configure these peripherals before entering PS1.

The functional characteristics of each of the active mode can be understood using the following table:

| Power State | PS4 Active | PS3 Active | PS2 Active | PS1 |

|---|---|---|---|---|

| CPU operating frequency (max) | 180 MHz | 90 MHz | 20 MHz or 32 MHz |

OFF |

| SRAM operating voltage | LDO SoC 1.1V | LDO SoC 1.0V | LDO SoC 0.7V or DC-DC 1.0V |

LDO SoC 0.7V or DC-DC 1.0V |

| Power domains ON | All | All |

|

|

| GPIOs available |

|

|

|

|

| SRAM powered ON |

|

|

|

|

Note: For more information on Power Domains, see the SiWx917 Hardware Reference Manual.

Standby States#

In Standby Mode, the M4 can enter PS4‑Standby, PS3‑Standby, or PS2‑Standby. You can enter Standby Mode from the corresponding Active state by using the Wait For Interrupt (WFI) instruction.

Standby characteristics include:

CPU clock is gated.

SRAM operates at the same voltage as in its corresponding Active state.

Peripherals, GPIOs, and SRAM availability match the corresponding Active state.

Any enabled interrupt can wake the M4 and return it to Active mode.

Sleep Mode Power States#

In Sleep Mode, the M4 can enter PS4‑Sleep, PS3‑Sleep, or PS2‑Sleep. Each power state can be entered from its respective Active state using software instructions. Sleep characteristics include:

CPU is power-gated

UULP peripherals are functional and must be configured before entering this state.

UULP-VBATT GPIOs remain powered.

320 KB LP-SRAM can be retained.

Deepsleep/Shutdown Mode#

PS0, also known as Deepsleep or Shutdown Mode, can be entered from any Active State through software instruction. Deepsleep/Shutdown mode characteristics include:

CPU is power-gated.

UULP peripherals are functional and must be configured before entering this state.

UULP-VBATT GPIOs are powered.

SRAM cannot be retained.

The flowchart below gives an overview on the power state transitions, CPU and SRAM configurations available in various power states.

Software can transition the M4 from any Active state to Standby, Sleep, or Shutdown.

Any enabled interrupt can wake the M4 from Standby, Sleep, or Shutdown and return it to Active mode.

M4 Power Save Wakeup Source#

The following table lists the wakeup sources available in Standby, Sleep, and Shutdown states.

| Wakeup Source | Wakeup Source, as present in the software | PS4/3/2 Standby | PS1 | PS4/3/2 Sleep | PS0 (Deep sleep) |

|---|---|---|---|---|---|

| Deep-Sleep Timer (DST) Interrupt | DST_BASED_WAKEUP | Yes | Yes | Yes | Yes |

| UULP VBAT GPIO | GPIO_BASED_WAKEUP | Yes | Yes | Yes | Yes |

| SYSRTC Interrupt | SYSRTC_BASED_WAKEUP | Yes | Yes | Yes | Yes |

| Alarm Interrupt | ALARM_BASED_WAKEUP | Yes | Yes | Yes | Yes |

| Second Interrupt | SEC_BASED_WAKEUP | Yes | Yes | Yes | Yes |

| Milli-Second | MSEC_BASED_WAKEUP | Yes | Yes | Yes | Yes |

| Watch Dog Interrupt | WDT_INTR_BASED_WAKEUP | Yes | Yes | Yes | Yes |

| Wireless Processor Interrupt | WIRELESS_BASED_WAKEUP | Yes (PS4/PS3 only) | Yes | Yes (PS4/PS3 only) | Yes |

| ULP Peripheral SDC (Sensor Data Collector) | SDCSS_BASED_WAKEUP | Yes | Yes | ||

| ULP Peripheral ADC/DAC Interrupt | ULPSS_BASED_WAKEUP | Yes | Yes | ||

| ULP timer interrupt | ULPSS_BASED_WAKEUP | Yes | Yes | ||

| ULP Touch Sensor Interrupt | |||||

| ULP GPIO Pin/ Group Interrupt | |||||

| ULP Peripheral DMA Interrupt | |||||

| ULP Peripheral ADC/DAC Interrupt | |||||

| ULP Peripheral UART Interrupt | |||||

| ULP Peripheral I2C Interrupt | |||||

| ULP Peripheral I2S Interrupt | |||||

| ULP Peripheral IR Interrupt | |||||

| ULP Peripheral SPI /SSI Interrupt |

Note: For more information on M4 Wakeup sources, see the SiWx917 SoC Hardware Reference Manual.