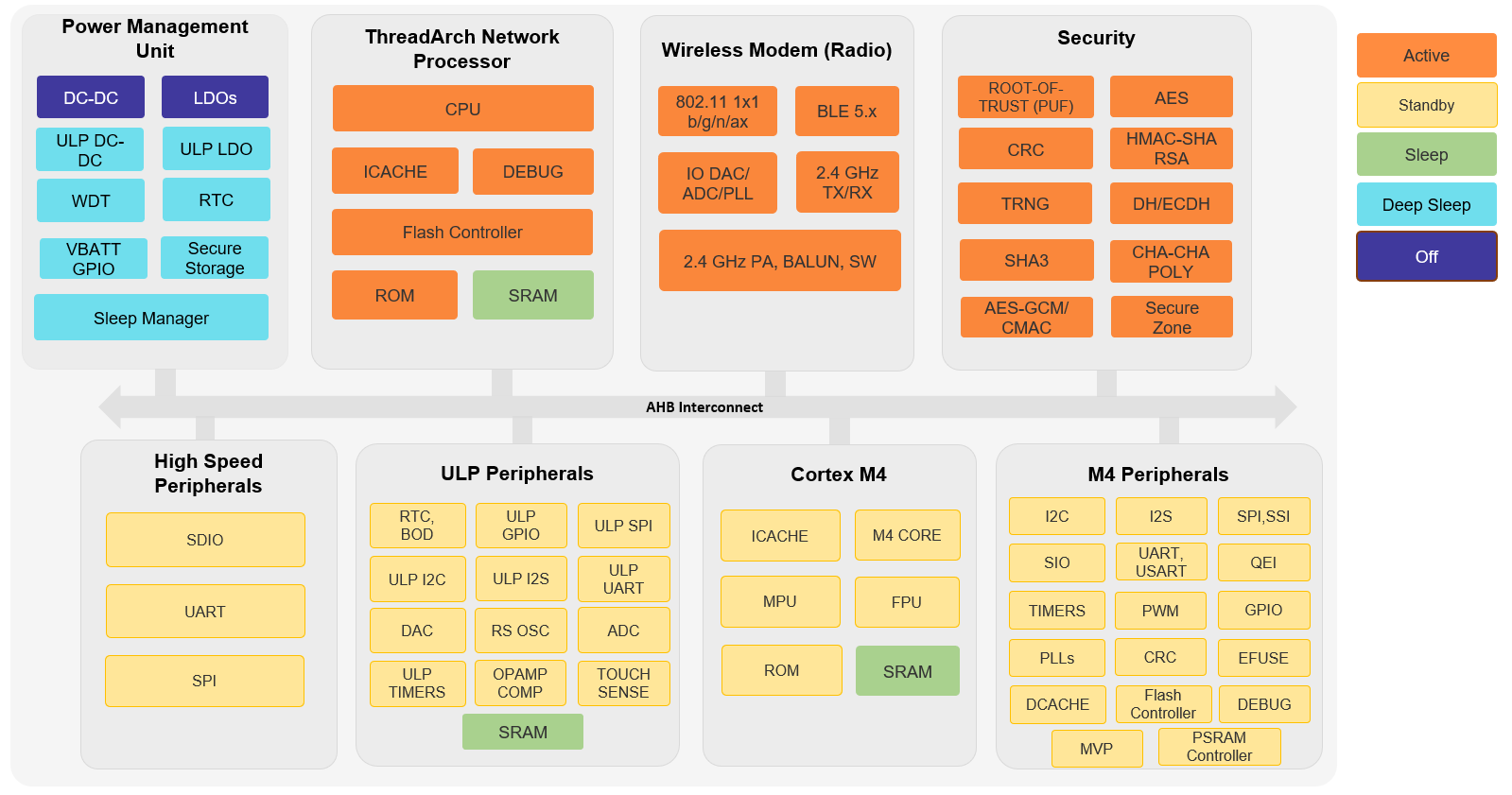

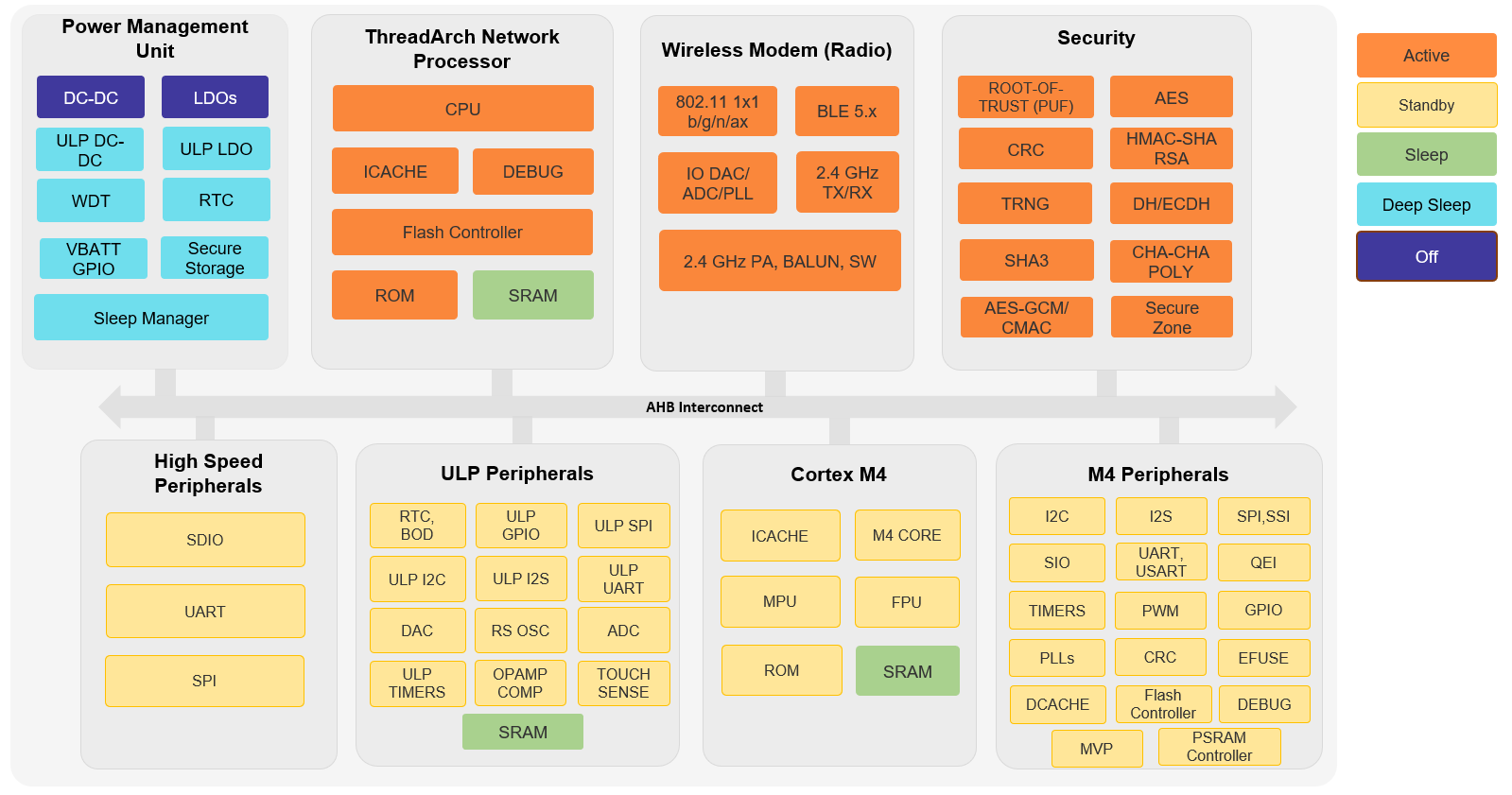

SiWx917 SoC Hardware Block Diagram#

The SiWx917 SoC includes the following functional blocks:

ThreadArch® Network Processor: A multi-threaded processor that runs wireless and network stacks on independent threads

Power Management Unit: Supplies power to the various domains of the SiWx917 chipset.

Wireless Modem (Radio): Integrates Wi-Fi, Bluetooth, the analog front end, a 2.4 GHz RF transceiver, and the built-in power amplifier subsystem.

Security: Includes security feature blocks such as hardware accelerators and secure firmware‑update.

Peripherals: Includes peripherals such as High-Speed peripherals, ULP peripherals, M4 peripherals.

Cortex-M4: A high-performance 32-bit processor that operates as the Microcontroller unit (MCU) of the device.

Note: Throughout this document, ThreadArch Network Processor, Cortex‑M4, and SiWx917 are referred to as NWP, M4, and SoC, respectively, for time brevity.

The SoC low power compatibility matrix can be illustrated as below:

| NWP Active | NWP Connected Sleep | NWP Unconnected Sleep with RAM Retention | NWP Unconnected Sleep without RAM Retention | |

|---|---|---|---|---|

| M4 Active (PS4/PS3/PS2) |  |

|

|

|

| M4 PS4/PS3/PS2 Standby |  |

|

||

| M4 PS4/PS3/PS2Sleep or PS1 |  |

|

||

| M4 Deepsleep (PS0) |  |

Run the M4 application or firmware from RAM in the following scenarios:

When the M4 is Active and the NWP is in Unconnected Sleep without RAM Retention mode.

When the M4 is in PS2 Active and the NWP is in either Active or Sleep mode.

Before you configure power‑save behavior for the combined SoC (M4 + NWP), understand how the M4 and the NWP manage power save independently.

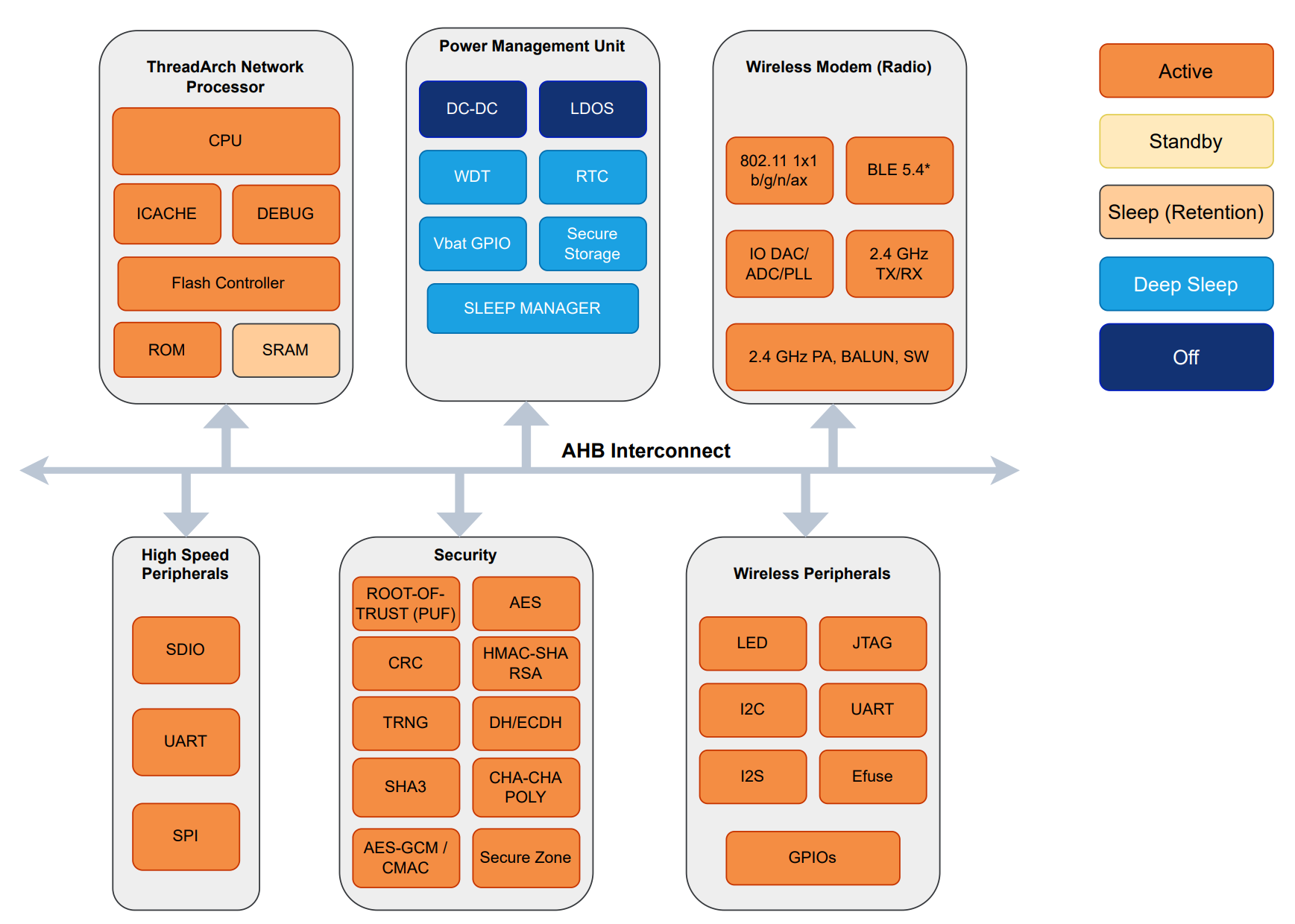

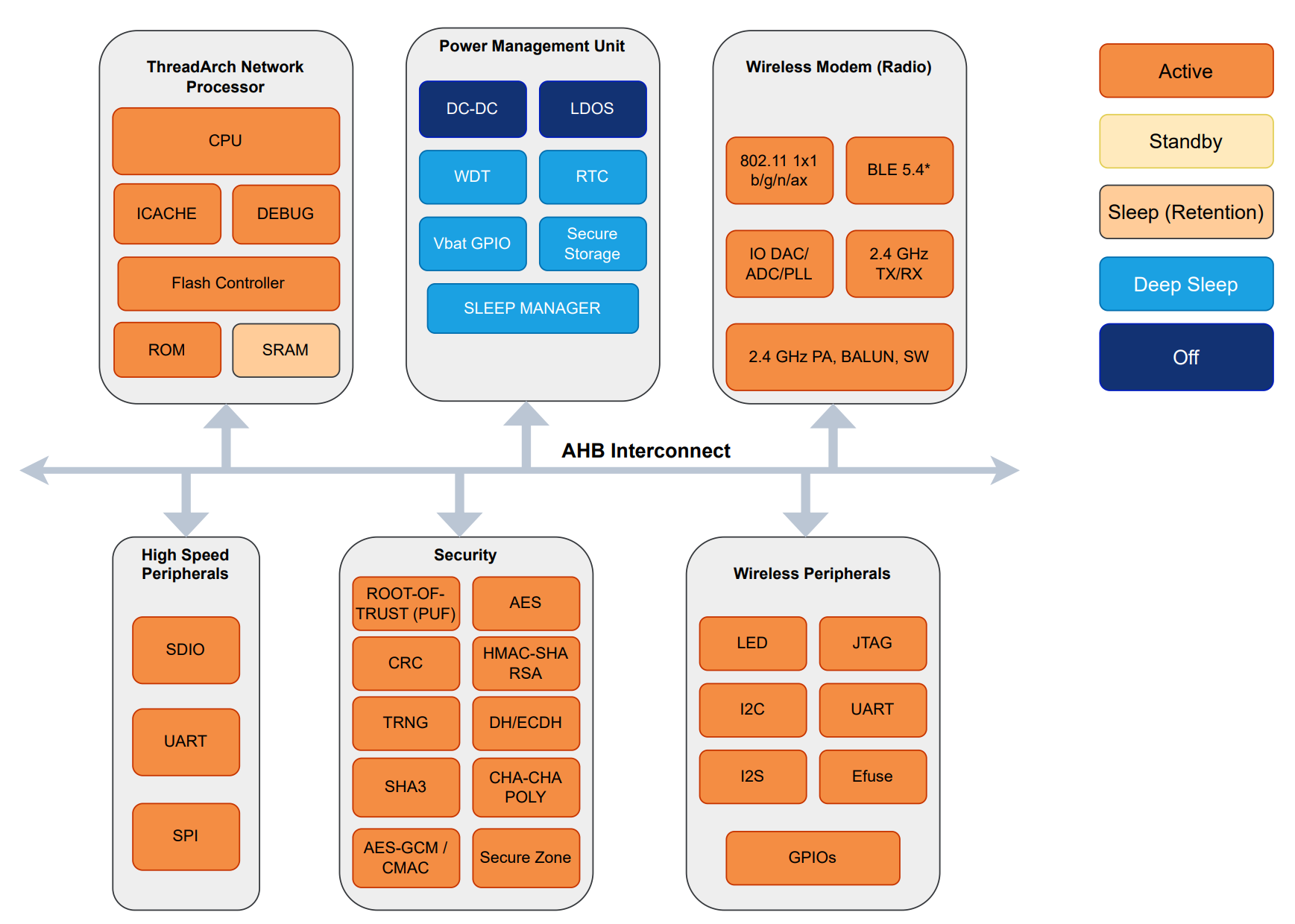

The SiWx917 NCP includes the following functional blocks:

ThreadArch Network Processor (NWP): A multi-threaded processor that runs wireless and network stacks on independent threads.

Power Management Unit (PMU): Supplies power to the various sections of the SiWx917.

Security: Includes security feature blocks such as hardware accelerators and secure firmware‑update.

Wireless Peripherals: Includes on‑chip peripherals such as LED, UART, and JTAG.

Host Interface Peripherals: Includes SDIO, UART, and SPI peripherals.